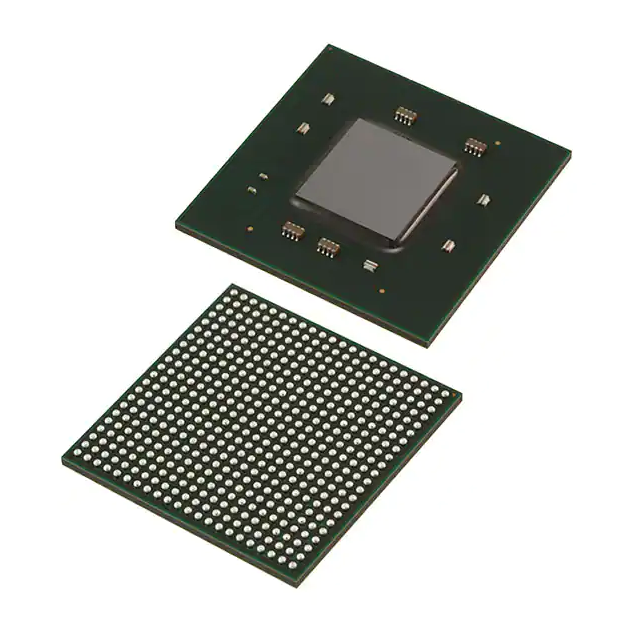

Нов и оригинален XC7A100T-2FGG484I IC интегрирано коло FPGA поле, програмабилна низа порти ad8313 IC FPGA 285 I/O 484FBGA

Атрибути на производот

| ТИП | ОПИС |

| Категорија | Интегрирани кола (IC)Вградени |

| Мфр | AMD Xilinx |

| Серии | Артикс-7 |

| Пакет | Послужавник |

| Стандарден пакет | 60 |

| Статус на производот | Активен |

| Број на LAB/CLBs | 7925 |

| Број на логички елементи/клетки | 101440 |

| Вкупно битови RAM меморија | 4976640 |

| Број на I/O | 285 |

| Напон – Напојување | 0,95 V ~ 1,05 V |

| Тип на монтирање | Површинска монтажа |

| Работна температура | -40°C ~ 100°C (TJ) |

| Пакет / Случај | 484-BBGA |

| Пакет со уреди за добавувач | 484-FBGA (23×23) |

| Основен број на производ | XC7A100 |

Користење на FPGA како сообраќајни процесори за мрежна безбедност

Сообраќајот до и од безбедносните уреди (заштитни ѕидови) е шифриран на повеќе нивоа, а шифрирањето/декрипцијата L2 (MACSec) се обработува во мрежните јазли на слојот за поврзување (L2) (прекинувачи и рутери).Обработката надвор од L2 (MAC слој) обично вклучува подлабоко парсирање, декрипција на тунелот L3 (IPSec) и шифриран SSL сообраќај со сообраќај TCP/UDP.Обработката на пакети вклучува парсирање и класификација на дојдовните пакети и обработка на големи количини на сообраќај (1-20 M) со висока пропусност (25-400 Gb/s).

Поради големиот број потребни компјутерски ресурси (јадра), НПУ може да се користат за обработка на пакети со релативно поголема брзина, но скалабилната обработка на сообраќајот со ниска латентност и високи перформанси не е можна бидејќи сообраќајот се обработува со помош на јадра MIPS/RISC и закажување такви јадра врз основа на нивната достапност е тешко.Употребата на безбедносни уреди базирани на FPGA може ефективно да ги елиминира овие ограничувања на архитектурите базирани на процесорот и NPU.

Обработка на безбедност на ниво на апликација во FPGA

FPGA се идеални за внатрешна безбедносна обработка во заштитните ѕидови од следната генерација бидејќи тие успешно ја задоволуваат потребата за повисоки перформанси, флексибилност и работа со мала латентност.Покрај тоа, FPGA може да имплементира безбедносни функции на ниво на апликација, што дополнително може да заштедат компјутерски ресурси и да ги подобрат перформансите.

Вообичаени примери за обработка на безбедноста на апликациите во FPGA вклучуваат

- TTCP истоварен мотор

- Сопирање на редовно изразување

- Асиметрична енкрипција (PKI) обработка

- Обработка на TLS

Безбедносни технологии од следната генерација кои користат FPGA

Бројни постоечки асиметрични алгоритми се ранливи на компромиси од квантните компјутери.Асиметричните безбедносни алгоритми како што се RSA-2K, RSA-4K, ECC-256, DH и ECCDH се најпогодени од техниките за квантно пресметување.Се истражуваат нови имплементации на асиметрични алгоритми и стандардизација на NIST.

Тековните предлози за пост-квантно шифрирање го вклучуваат методот Учење со прстен по грешка (R-LWE) за

- Криптографија со јавен клуч (PKC)

- Дигитални потписи

- Создавање клуч

Предложената имплементација на криптографијата со јавен клуч вклучува одредени добро познати математички операции (TRNG, гаусовиот семплер на шум, собирање на полином, делење квантификатор на бинарен полином, множење итн.).FPGA IP за многу од овие алгоритми е достапна или може ефикасно да се имплементира со користење на FPGA градежни блокови, како што се моторите DSP и AI (AIE) во постојните и уредите од следната генерација на Xilinx.

Оваа бела книга ја опишува имплементацијата на безбедноста L2-L7 со помош на програмабилна архитектура која може да се користи за забрзување на безбедноста во мрежите за раб/пристап и заштитни ѕидови од следната генерација (NGFW) во мрежите на претпријатијата.